International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

# An Efficient Data Approximation Framework for Network on Chip Architectures

R.Poovendran<sup>1</sup>, M.H.Rajarajeshwari<sup>2</sup>, M.Swathi<sup>3</sup>, N.Triveni<sup>4</sup>, S.Uthayakala<sup>5</sup>

Associate Professor, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India<sup>1</sup>

U.G. Student, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India<sup>2,3,4,5</sup>

**ABSTRACT**: The pattern of unsustainable power utilization and vast memory transmission limit requests in tremendously parallel multi-core systems. Enormous information time which brings an other calculation demonstrate for approximate computing. The Approximate computing technique comprises of ACA adder incorporates mistake recognition and remedy hardware, which is appropriate for low power IC structure however it expands the zone and deferral. To conquer the disadvantage of ACA adder, Reconfigurable carry look-a head Adder is utilized which is predominant then different Adders regarding speed and decrease of area. Thus, inexact coordinating of information is utilized to diminish the transmission of roughly comparative information in the NOC propose another Reconfigurable estimated convey look-ahead adder. There by lessening region, power and delay. This proposed NOC Architecture is simulated utilizing xilinx12.1

**KEYWORDS**: Multicore framework, Approximate computing, Network on Chip, Reconfigurable Carry lookahead Adder.

# I.INTRODUCTION

Evaluated enlisting is a promising system for low power IC plot which reestablishes a maybe incorrect result rather than guaranteed exact result. This calculation technique can be used for a few applications, for instance, sound, video, haptic getting ready and machine acknowledging where a harsh result is satisfactory for its inspiration. For such error tolerant applications are found in riches in rising progressions and applications. In a couple of inaccurate adder diagrams have been created.

Network-on-Chip is a correspondence subsystem on a integrated circuit. It is normally between IP cores in a SoC. The Network-on-Chip innovation applies on-chip specialized techniques. It is a dependable and adaptable correspondence worldview regarded as an option in contrast to exemplary transport system in current System-on-chip. In the idea of reconfigurable Network-on-Chip that present self-versatile systems in Network-on-Chips. This self-versatile system is progressively productive and adaptable and furthermore pertinent for self-upgrading, self-mending and self-securing. The plan objectives for Network-on-Chips can be portrayed as stage based structure, detachment among correspondence and figuring asset, decreasing territory and vitality. Gauge can diminish control use with mixed up circuit.

ACA adder for which the exactness of results is configurable in the midst of runtime by virtue of its configurability; ACA adder can work both surmised mode and accurate mode. More summed up interpretation of ACA, called Generic Accuracy Configurable Adder [1]. Proposed another exactness configurable adder circuit, which is like ACA in creating the primary inexact outcome, yet in this way we enhance the precision

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization Volume 8, Special Issue 1, March 2019 7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

# 19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

over pipeline stages beginning from the Most Significant Bit (MSB) first. Because of this, get enormous enhancement in precision just inside the initial couple of phases of the blunder amendment pipeline [2]. Proposed a precision configurable adder circuit called Gracefully-debasing adder (GDA). Which takes into account reconfigurable sub-adder widths convey chain thought amid runtime. It has no amendment unit [3]. Proposed a Simple Accuracy Reconfigurable Adder plan, it is a pass on desire based exactness configurable adder layout with less area stand out from CLA. Diverge from agilely debasement adder, essential accuracy reconfigurable adder realizes half less power-delay-thing and can achieve a comparative peak signal to noise ratio(PSNR). In the defer delay-flexible reconfiguration framework in like manner improve the precision control concede exchange off [4].

Proposed a Dynamic programming-based life time mindful directing calculations to enhance the lifetime dependability of Network-on-Chip switches [5]. The utilization of a reconfigurable switch, where the cradle spaces are progressively dispensed to build switch effectiveness in a Network-on-Chip, even under rather extraordinary correspondence loads [6]. In this paper, propose a Reconfigurable Approximate Carry Look-Ahead Adder. It has two working techniques for right and assessed. In this structure of the adder relies upon the right pass on look-ahead adder. For the right incorporate action does not require an external change unit. In this Reconfigurable CLA adder fundamentally more diminutive postponement, zone and power in evaluated mode appear differently in relation to other sort of adder[7].

# II. RELATED WORK

#### A. XY ALGORITHM:

XY routing algorithm goes under deterministic directing calculation. This calculation can be actualized for both for ordinary and unpredictable system topology. It is called dimensionorder routing (DOR). It pursues the idea of negligible turning directing. In this directing every hub or switch of NoC is recognized by the (x, y)co-ordinates of that hub for a 2D mesh[8]. As per this algorithm the information packets will cross in X-heading towards the goal segment. Subsequent to finding the goal segment the data packets will navigate to the goal hub. Information development in this calculation is portrayed in a precedent in Figure. This calculation just expresses that "First the information willmove in X-course and after that in Y-heading". That is the reason the name of the calculation is XY Routing algorithm[9]. As per this calculation the packets can't move first in Y-bearing then in X-course. So it makes them defeat or turning limitations. Because of which it moves toward becoming stop free. As indicated by this calculation, (x, y) organize of Current switch is contrasted with the (x, y) arrange of Destination router[10]. In the event that they are equivalent, this will demonstrate information parcels have achieved its goal and they will be steered to the asset through the neighbourhood port. On the off chance that they are not equivalent, the x-facilitate of goal is at first contrasted with the x-arrange of current switch. At the point when x-organize of currentrouter is not as much as x-facilitate of goal switch, the information parcels will be transmitted toward the East bearing, when x-arrange of current switch is more prominent than x-facilitate of goal switch, at that point packets will be steered to West course. At that point check if the information bundle is as of now on the goal segment or not[11]. On the off chance that this last condition is valid, the vertical location of goal is contrasted with the vertical location of current switch. Information bundles will be crossed to South heading when vertical location of current switch is not exactly vertical location of goal switch, to North when vertical location of current switch is more noteworthy than goal router[12].

#### **B. ACCURACY CONFIGURABLE ADDER:**

Around there consider the exactness configurable adder circuits to play out the number juggling action by covering sub-adders to diminish errors from pass on truncation N and K is the two particular framework

# International Journal of Innovative Research in Science, Engineering and Technology An ISO 3297: 2007 Certified Organization Volume 8, Special Issue 1, March 2019 7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19) 19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

## Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

parameters in ACA adder[13]. N is the length of sub-adder and 2K bits wide for each sub-adder. Consider N=20 and K=4 in The total number of sub-adders are figure by using underneath M=(N/K)-1.

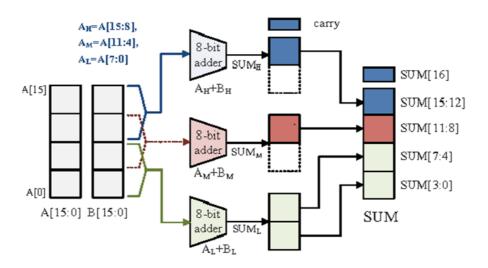

Figure. 1 demonstrates precision configurable adder, which has four sub-adders S0 to S3 and each sub-adder is 8-bits when the convey is more prominent than k bits. At that point the sub-adder missed the carry.So, the yield isn't right to address that blunder yield ought to be increased by 1[14].The mistake rectification is begin from least huge sub-adder to most critical sub-adder. ACA adder experiences some downside that the early amendment methods in the pipeline stages are little in size and they are performed from the least significant bit[15].

Fig. 1.Accuracy configurable Adder

#### C. GRACEFULLY-DEGRADING ACCURACY CONFIGURABLE ADDER:

In this area, talk about gracefully debasing precision configurable adder plan[16]. This adder comprises of four phases, every one of the phases to be performed if the most noteworthy bits of the outcomes. Consider N-bit GDA adder and two N-bit addends An and B and use snake units to get the divided numbers to be added. Where, Ai and Bi are the ith bit of A and B, spread P, and produce G as pursues:

# Pi=Ai ⊕Bi Gi=Ai. Bi Ci+1=Gi+ Pi. Ci

Multiplexers are utilized to interface adder units and convey in chooses from either least critical adder unit or convey in forecast segment. The issue of reconfiguring GDA adder into certain mode is equivalent to the issue of consolidating adder units into certain sub-adders and experience the ill effects of low precision loss. The convey in forecast is hard to decide precision of surmised adders and the exactness setup component are utilized to reconfigure the quantity of convey expectation bits. The usage of convey in expectation is perplexing however exact one. In writing work different sorts' convey in expectation plans are proposed. GDA adder experience the ill effects of a few downsides, it has no blunder rectification and identification plot, can't be pipelined. In the Table.1.results in high exactness of more prominent delay[17].

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

# 19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

## **III. PROPOSED WORK**

The Network-on-Chip technology applies networking theory and on-chip communication methods. It is a reliable and scalable communication paradigm deemed as an alternative to classic bus system in modern system -on- chip.

| Methods | Probability of error | Probability of error by |

|---------|----------------------|-------------------------|

|         |                      | simulation              |

| GeAr    | 2.9297%              | 2.9480%                 |

| Accurus | 96.98%               | 94.13%                  |

• Router:A router or switch is a frameworks organization contraption that progresses data distributes PC frameworks. Changes play out the development planning limits on the Internet. It has altogether a greater number of capacities than other framework contraptions, for instance, a switch or focus that are simply prepared to perform major framework capacities[18].

• IP Core:IP Core or IP square is a reusable unit of method of reasoning, cell or consolidated circuit group structure that is the ensured advancement of one social event. IP Cores can be used as building hinder inside application specific composed circuit.

• Network Interface: A system interface is commonly a system interface card (NIC). A organize interface is the purpose of interconnection between a PC and a private or open system .

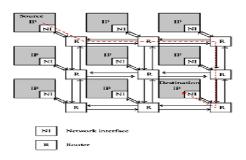

Fig 2 NOC structure

Propose reconfigurable packed information – RDNoCs, an information approximation system for Network-on-Chips to ease the effect of substantial information correspondence worry by utilizing the mistake resilience of utilizations. To lessen the transmission of roughly comparable information in the Network-on-Chip propose another configurable exactness tuning adder. In this paper, propose a Reconfigurable Approximate Carry Look-Ahead Adder.Fig.2, shows NoC Architecture. It has two working strategies for right and estimated. In this structure of the adder relies upon the right pass on lookaheadadder. For the right incorporate action does not require an external change unit[19]. In this right CLA adder essentially more diminutive postponement, territory and power in assessed mode diverge from other sort of adder.

## Si=Pi ⊕Ci Ci+1=Gi + Pi Ci

# International Journal of Innovative Research in Science, Engineering and Technology An ISO 3297: 2007 Certified Organization Volume 8, Special Issue 1, March 2019 7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19) 19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

Where Ci is the input carry and Pi and Gi are the propagate  $(Ai \oplus Bi)$  and generate (Ai Bi) signals of the ith stage.

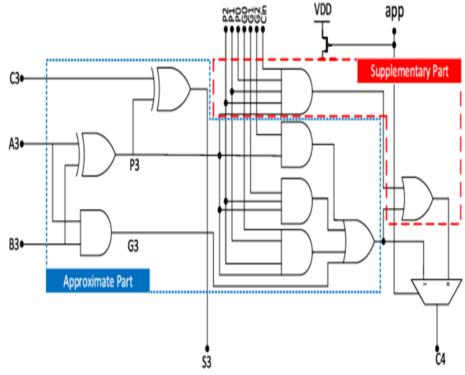

Fig 3 Proposed reconfigurable approximate carry look-ahead adder

In the above Fig.3., shows the proposed Reconfigurable Approximate Carry Look-Ahead Adder structure. The structure of left part is approximate part and right part is augmenting part. Both of these parts are used to calculate the carry output[20]. For the proposed reconfigurable approximate adder based on this segmentation, two exact and approximate operating modes are realized. In this circuit, only one multiplexer is added compared to the exact CLA.

#### IV. RESULTS AND DISCUSSION

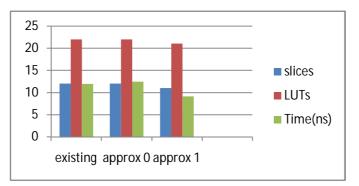

In this area, first unique structure parameters of the proposed adder of with and without blunder decrease unit and our proposed adder (Reconfigurable approximate convey look-ahead adder) are considered. Nonexclusive Accuracy Configurable Adder gives more plan conceivable outcomes contrasted with effortlessness completely corrupting exactness configurable adder. Some Configurable adders, for example, ACA and GeAr , actualize mistake revision with pipelining, to get the total outcome which some of the time takes various clock cycles.By utilizing table 2,table 3,table 4, the outcomes incorporate both rough and accurate working modes. The outcomes for the deferral, territory and intensity of the 16-bit estimated adder have been accounted .Fig.4 shows Performance results

# International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

# 19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

## XILINX SYNTHESIS REPORT

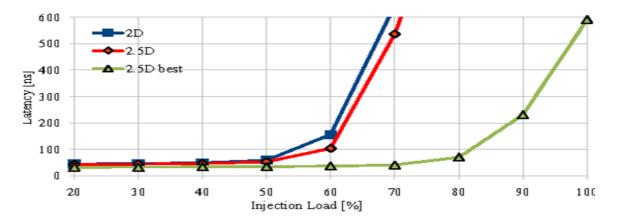

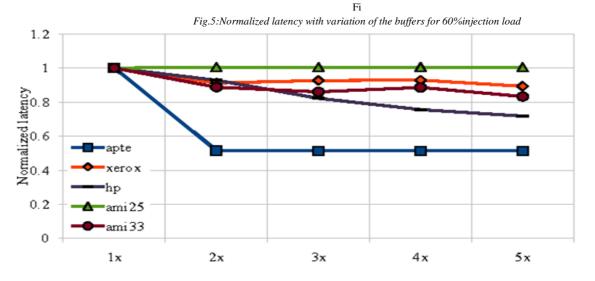

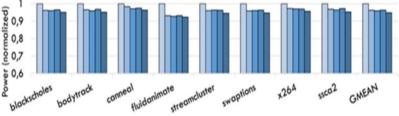

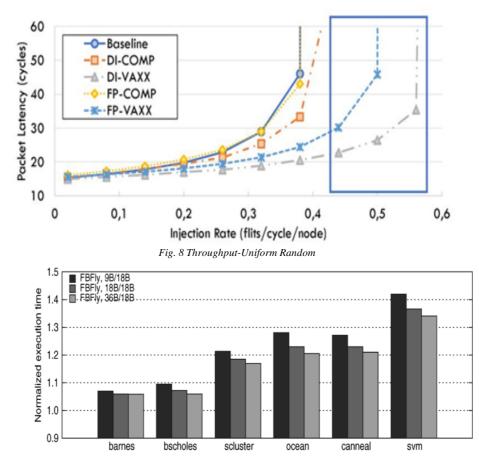

The proposed Adder circuit has been simulated and the synthesis report obtained by using Xilinx ISE 12.1i. The various parameters used for computing existing and proposed systems with Spartan-3 processor are listed below. Fig.5 shows Normalized latency with variation of the buffers for 60% injection load. Fig.6 shows Latency control.Fig.7 shows Power consumption and Area Overhead.Fig.8 shows Throughput-Uniform Random. Fig.9 shows Performance for the baseline 64-core CMP.

| Table.2.Design summary of existing |      |           |             |  |  |  |

|------------------------------------|------|-----------|-------------|--|--|--|

| Logic utilization                  | Used | Available | Utilization |  |  |  |

| Number of Slices                   | 12   | 960       | 1%          |  |  |  |

| Number of 4 input LUTs             | 22   | 1920      | 1%          |  |  |  |

| Number of bonded IOBs              | 26   | 66        | 39%         |  |  |  |

Path delay: 11.090ns

| Table.3.Design summary of proposed with approx. 0 |      |           |             |  |  |  |

|---------------------------------------------------|------|-----------|-------------|--|--|--|

| Logic utilization                                 | Used | Available | Utilization |  |  |  |

| Number of Slices                                  | 12   | 960       | 0%          |  |  |  |

| Number of 4 input LUTs                            | 22   | 1920      | 0%          |  |  |  |

| Number of bonded IOBs                             | 26   | 66        | 39%         |  |  |  |

Path delay: 12.427ns

| Logic utilization      | Used | Available | Utilization |

|------------------------|------|-----------|-------------|

| Number of Slices       | 11   | 960       | 1%          |

| Number of 4 input LUTs | 21   | 1920      | 1%          |

| Number of bonded IOBs  | 26   | 66        | 39%         |

Path delay: 9.082ns

Fig.4.Performance results

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

Fig.6.Latency control

Baseline DI-COMP DI-VAXX FP-COMP FP-VAXX

Fig. 7 Power consumption and Area Overhead

1

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

# 19<sup>th</sup>-20<sup>th</sup> March 2019

#### Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

Fig. 9: Performance for the baseline 64-core CMP

#### V. CONCLUSION

In this work encourages surmised coordinating of information, to lessen the transmission of roughly comparative information in the Network-On-Chip. In this paper propose another Reconfigurable approximate carry look-ahead adder. The adder enchanted the limit of exchanging among surmised and accurate working modes. In Fig.4., survey the effectiveness of the proposed structure its plan parameters were contrasted with those of some suggested reconfigurable approx adders. The parameters which included defer area and power were assessed.

#### REFERENCES

[1] VinamraBenara, Suresh Purini, "Accurus: A Fast Convergence Technique forAccuracy Configurable Approximate Adder Circuits," in proc.IEEE Computer Society AnnualSymposium on VLSI,July 2016, pp. 577-582.

<sup>[2]</sup> Mohammed Shafique ,Waqas Ahmad, Rehan Hafiz, Jorg Henkel, "Low latency generic accuracy configurable adder", in proc. Design Autom.Conf.(DAC), 2015, pp.1-6.

<sup>[3]</sup> Rong Ye, Ting Wang, Feng Yuan, Rakesh Kumar and QiangXu, "On Reconfigurable-Oriented approximate adder design and its application," in Proc. Int. Conf. Computer-Aided Design (ICCAD), 2013, pp. 48-54.

<sup>[4]</sup> WenbinXu, Sachin S. Sapatnekar, Jiang Hu, "A Simple Yet Efficient Accuracy-Configurable Adder Design,"IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2018.

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

# 19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

- [5] Liang Wang, Xiaohang Wang, Terrence Mak, "Adaptive Routing Algorithms for Lifetime Reliability Optimization in Network-on-Chip," IEEE Journal of Latex Class Files, 2012.

- [6] Débora Matos, Caroline Concatto, MárcioKreutz, Fernanda Kastensmidt, Luigi Carro, AltamiroSusin Y. Yorozu, M. Hirano, "Reconfigurable Routers for Low power and High Performance," IEEE Transaction On Very Large Scale Integration (VLSI) System, 2011.

- Sarzamin Khan, SherazAnjum, Usman Ali Gulzar, Frank Sill Torres, "Comparative analysis of network-on-chip simulation tools", IET Computers & Digital Technique, 2018, Vol. 12 Issue. 1, pp. 30-38.

- [8] Poovendran.Rand S.Sumathi, "An Low-Power Area-Efficient Routing Analysis and Optimization for a Fat Tree-Based Optical Network-On-chip(ONoC) Architectures", Sensor Letters- American Scientific Publishers", vol.16, Issue 11, page 862-876, March 2018

- [9] Poovendran.Rand S.Sumathi, "An Area-Efficient FPGA Implementation of Network-on-Chip(NoC) Router Architecture for Optimized Multicore-SoC Communication", Sensor Letters- American Scientific Publishers" vol 16, Page 552-560, March 2018.

- [10] Poovendran.R and S.Sumathi, "An Area-Efficient Low-Power SCM Topology for High Performance Network-on Chip(NoC) Architecture using an Optimized Routing Design', International Journal of Concurrency and Computation: Practice and Experience -Wiley Blackwell publishers, DOI:10.1002/cpe.4760, 2018.

- [11] David A. Bader and KameshMadduri. 2005. Design and Implementation of the HPCSGraphAnalysisBenchmarkonSymmetricMultiprocessors.InProceedings of the 12th International Conference on High Performance Computing (HiPC 2005). 465–476.

- [12] Christian Bienia. 2011. Benchmarking Modern Multiprocessors. Ph.D. Dissertation. Princeton University.

- [13] NathanBinkert, Bradford Beckmann, Gabriel Black, Steven K. Reinhardt, Ali Saidi, ArkapravaBasu, JoelHestness, DerekR. Hower, Tushar Krishna, SomayehSardashti, RathijitSen, Korey Sewell, Muhammad Shoaib, NilayVaish, Mark D. Hill, and David A. Wood. 2011. The Gem5 Simulator. SIGARCH Comput. Archit. News 39 (2011), 1–7.

- [14] M. Creel and M. Zubair. 2012. High Performance Implementation of an Econometrics and Financial Application on GPUs. In Proceedings of International Conference on High Performance Computing, Networking, Storage and Analysis (SCC 2012). 1147– 1153.

- [15] Reetuparna Das, Asit K. Mishra, ChrysostomosNicopoulos, Dongkook Park, Vijaykrishnan Narayanan, Ravishankar R. Iyer, Mazin S. Yousif, and Chita R. Das. 2008. Performance and Power Optimization Through Data Compression in Network-on-Chip Architectures. In Proceedings of the 14th International Conference on High-Performance Computer Architecture (HPCA-14). 215– 225.

- [16] Zidong Du, AvinashLingamneni, Yunji Chen, Krishna V. Palem, Olivier Temam, and Chengyong Wu. 2015. Leveraging the Error Resilience of Neural Networks for Designing Highly Energy Efficient Accelerators. IEEE Trans. on CAD of Integrated Circuits and Systems 34 (2015), 1223–1235.

- [17] HadiEsmaeilzadeh, Adrian Sampson, Luis Ceze, and Doug Burger. 2012. Architecture Support for Disciplined Approximate Programming. SIGPLAN Not. 47, 4 (2012), 301–312.

- [18] SwagathVenkataramani, Vinay K. Chippa, Srimat T. Chakradhar, Kaushik Roy, and AnandRaghunathan. 2013. Quality Programmable Vector Processors for Approximate Computing. In Proceedings of the 46th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO-46). 1–12.

- [19] Amir Yazdanbakhsh, Jongse Park, Hardik Sharma, PejmanLotfi-Kamran, and HadiEsmaeilzadeh. 2015. Neural Acceleration for GPU Throughput Processors. In Proceedings of the 48th International Symposium on Microarchitecture (MICRO-48). 482–493.

- [20] J. Zhan, M. Poremba, Y. Xu, and Y. Xie. 2014. Leveraging Delta Compression for End-to-End Memory Access in NoC Based Multicores. In 2014 19th Asia and South Pacific Design Automation Conference (ASP-DAC). 586–591.